# Development of a Fault Injection-Based Dependability Assessment Methodology for Digital I&C Systems

Volume 3

Office of Nuclear Regulatory Research

#### AVAILABILITY OF REFERENCE MATERIALS IN NRC PUBLICATIONS

#### **NRC Reference Material**

As of November 1999, you may electronically access NUREG-series publications and other NRC records at NRC's Public Electronic Reading Room at <u>http://www.nrc.gov/reading-rm.html.</u> Publicly released records include, to name a few, NUREG-series publications; *Federal Register* notices; applicant, licensee, and vendor documents and correspondence; NRC correspondence and internal memoranda; bulletins and information notices; inspection and investigative reports; licensee event reports; and Commission papers and their attachments.

NRC publications in the NUREG series, NRC regulations, and Title 10, "Energy," in the *Code of Federal Regulations* may also be purchased from one of these two sources.

- The Superintendent of Documents

U.S. Government Printing Office Mail Stop SSOP

Washington, DC 20402–0001

Internet: bookstore.gpo.gov

Telephone: 202-512-1800

Fax: 202-512-2250

The National Technical Information Service

- 2. The National Technical Information Service Springfield, VA 22161–0002 www.ntis.gov 1–800–553–6847 or, locally, 703–605–6000

A single copy of each NRC draft report for comment is available free, to the extent of supply, upon written request as follows:

Address: U.S. Nuclear Regulatory Commission Office of Administration Publications Branch Washington, DC 20555-0001 E-mail: DISTRIBUTION.RESOURCE@NRC.GOV

Facsimile: 301-415-2289

Some publications in the NUREG series that are posted at NRC's Web site address

http://www.nrc.gov/reading-rm/doc-collections/nuregs are updated periodically and may differ from the last printed version. Although references to material found on a Web site bear the date the material was accessed, the material available on the date cited may subsequently be removed from the site.

#### Non-NRC Reference Material

Documents available from public and special technical libraries include all open literature items, such as books, journal articles, transactions, *Federal Register* notices, Federal and State legislation, and congressional reports. Such documents as theses, dissertations, foreign reports and translations, and non-NRC conference proceedings may be purchased from their sponsoring organization.

Copies of industry codes and standards used in a substantive manner in the NRC regulatory process are maintained at—

The NRC Technical Library Two White Flint North 11545 Rockville Pike Rockville, MD 20852–2738

These standards are available in the library for reference use by the public. Codes and standards are usually copyrighted and may be purchased from the originating organization or, if they are American National Standards, from—

American National Standards Institute 11 West 42<sup>nd</sup> Street New York, NY 10036–8002 www.ansi.org 212–642–4900

Legally binding regulatory requirements are stated only in laws; NRC regulations; licenses, including technical specifications; or orders, not in NUREGseries publications. The views expressed in contractor-prepared publications in this series are not necessarily those of the NRC.

The NUREG series comprises (1) technical and administrative reports and books prepared by the staff (NUREG–XXXX) or agency contractors (NUREG/CR–XXXX), (2) proceedings of conferences (NUREG/CP–XXXX), (3) reports resulting from international agreements (NUREG/IA–XXXX), (4) brochures (NUREG/BR– XXXX), and (5) compilations of legal decisions and orders of the Commission and Atomic and Safety Licensing Boards and of Directors' decisions under Section 2.206 of NRC's regulations (NUREG–0750).

**DISCLAIMER:** This report was prepared as an account of work sponsored by an agency of the U.S. Government. Neither the U.S. Government nor any agency thereof, nor any employee, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for any third party's use, or the results of such use, of any information, apparatus, product, or process disclosed in this publication, or represents that its use by such third party would not infringe privately owned rights.

Protecting People and the Environment

# Development of a Fault Injection-Based Dependability Assessment Methodology for Digital I&C Systems

## Volume 3

Manuscript Completed: November 2011 Date Published: December 2012

Prepared by: C. R. Elks, N. J. George, M. A. Reynolds, M. Miklo, C. Berger, S. Bingham, M. Sekhar, B. W. Johnson

The Charles L. Brown Department of Electrical and Computer Engineering The University of Virginia Charlottesville, Virginia

NRC Project Managers: S. A. Arndt, J. A. Dion, R. A. Shaffer, M. E. Waterman

NRC Job Code N6214

Prepared for: Division of Engineering Office of Nuclear Regulatory Research U.S. Nuclear Regulatory Commission Washington, DC 20555-0001

NUREG/CR-7151, Vols. 1 to 4 have been reproduced from the best available copy.

## ABSTRACT

Today's emergent computer technology has introduced the capability of integrating information from numerous plant systems and supplying needed information to operations personnel in a timely manner that could not be envisioned when previous generation plants were designed and built. For example, Small Modular Reactor (SMR) plant designs will make extensive use of computer based I&C systems for all manner of plant functions, including safety and non-safety functions. On the other hand, digital upgrades in existing light water reactor plants are becoming necessary in order to sustain and extend plant life while improving plant performance, reducing maintenance costs of aging and obsolete equipment, and promoting prognostic system monitoring and human machine interface (HMI) decision making.

The extensive use of digital instrumentation and control systems in new and existing plants raises issues that were not relevant to the previous generation of analog and rudimentary digital I&C systems used in the 1970's style plants. These issues include the occurrence of unknown failure modes in digital I&C systems and HMI issues. Therefore, digital system reliability/safety, classification of digital I&C system failures and failure modes, and software validation remain significant issues for the Light Water Sustainability and SMR initiatives and the digital I&C system community at large.

The purpose of the research described in volume 1 thru volume 4 is to help inform the development of regulatory guidance for digital I&C systems and potential improvement of the licensing of digital I&C systems in NPP operations. The work described herein presents; (1) the effectiveness of fault injection (as applied to a digital I&C system) for providing critical safety model parameters (e.g., coverage factor) and system response information required by the PRA and reliability assessment processes, (2) the development and refinement of the methodology to improve applicability to digital I&C systems, and (3) findings for establishing a basis for using fault injection as applied to a diverse set of digital I&C platforms. Some of the specific issues addressed in Volume 1 are:

- Fault Injection as a support activity for PRA activities.

- Development of the UVA fault injection based methodology.

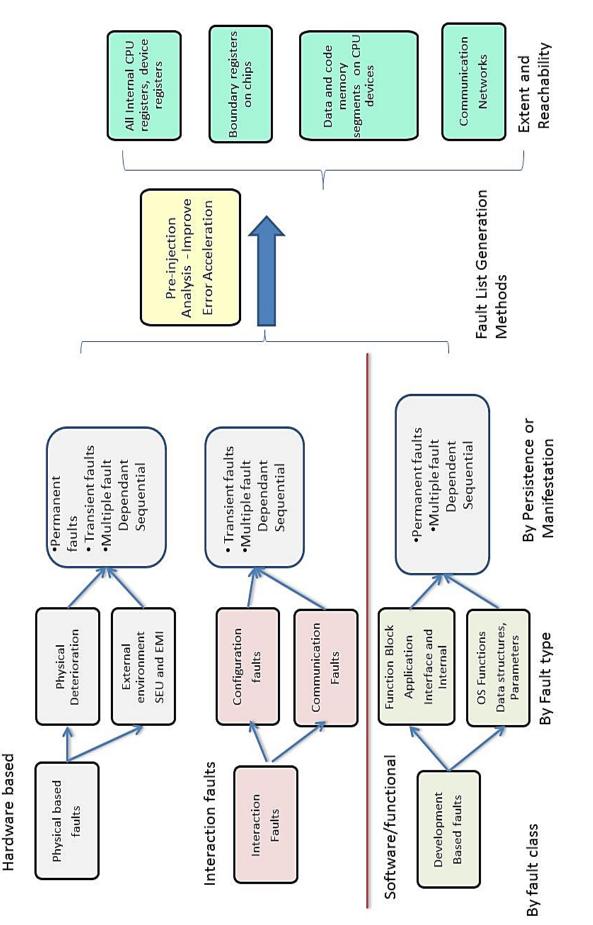

- Fault models for contemporary and emerging IC technology in Digital I&C Systems.

- Requirements and challenges for realizing Fault Injection in Digital I&C systems.

- Solutions to challenges for realizing fault injection in digital I&C systems.

Volume 1 presents the findings of developing a fault injection based quantitative assessment methodology with respect to processor based digital I&C systems for the purpose of evaluating the capabilities of the method to support NRC probabilistic risk assessment (PRA) and review of digital I&C systems. Fault injection is defined as a dependability validation technique that is based on the realization of controlled validation experiments in which system behavior is observed when faults are explicitly induced by the deliberate introduction (injection) of faults into the system [Arlat 1990]. Fault injection is therefore a form of *accelerated testing* of fault tolerance attributes of the digital I&C system under test.

Volumes 2 and 3 of this research present the application of this methodology to two commercial-grade digital I&C system executing a reactor protection shutdown application.

In Volumes 2 and 3, the research identified significant results related to the operational behavior of the benchmark systems, and the value of the methodology with respect to providing data for the quantification of dependability attributes such as safety, reliability, and integrity. By applying a fault injection-based dependability assessment methodology to a commercial grade digital

I&C, the research provided useful evidence toward the capabilities and limitations of fault injection-based dependability assessment methods with respect to modern digital I&C systems. The results of this effort are intended to assist NRC staff determine where and how fault injection-based methodologies can best fit into the overall license review process.

The cumulative findings and recommendations of both applications of the methodology and application of the generalized results to broader classes of digital I&C systems are discussed in volume 4.

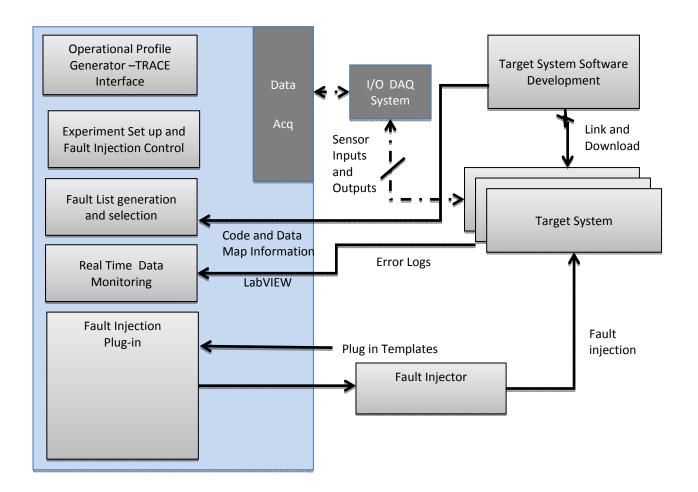

The digital I&C systems under test for this effort, herein defined as Benchmark System I and Benchmark System II, are fault tolerant multi-processor safety-critical digital I&C systems typical of what would be used in a nuclear power plant 1-e systems. The benchmark systems contain multiple processing modules to accurately represent 4 channel or division 2 out of 4 reactor protection systems. In addition, the systems contain a redundant discrete digital input and output modules, analog input and output modules, inter-channel communication network modules, other interface modules to fully represent and implement a Reactor Protection System. The application Reactor Protection System software was developed using the benchmark systems software development and programming environments.

To establish a proper operational context for the fault injection environment a prototype operational profile generator tool based on the US NRC systems analysis code TRACE [NRC 2011] was developed. This tool allowed generation of realistic system sensor inputs to the Reactor Protection System (RPS) application based on reactor and plant dynamics of the simulated model. In addition, the tool allowed creation of accident events such as large break LOCAs, turbine trips, etc., to stress the RPS application under the various design basis events.

#### Bibliography

[NRC 2001]Commission, U.S. Nuclear Regulatory. Computer Codes. April 2011.<br/>http://www.nrc.gov/about-nrc/regulatory/research/comp-codes.html<br/>(accessed 2011).[Arlat 1990]J. Arlat, M. Aguera, et. al. "Fault Injection for Dependability Evaluation: A<br/>Methodology and Some Applications." IEEE Transactions on Software<br/>Engineering, February 2, 1990.

## FOREWORD

As discussed in the NRC Policy Statement on Probabilistic Risk Assessment (PRA), the NRC intends to increase its use of PRA methods in all regulatory matters to the extent supported by state-of-the-art PRA methods and data. Currently, I&C systems are not modeled in PRAs. As the NRC moves toward a more risk-informed regulatory environment, the staff will need data, methods, and tools related to the risk assessment of digital systems. Fault injection methods can provide a means to estimate quantitatively the behavior model parameters of the system. The quantification of these parameters (in a probabilistic sense) can be used to produce more accurate parameter estimates for PRA models, which in turn produces more a accurate risk assessment to inform the risk oversight process.

A challenge for evaluating system reliability relates to relatively undeveloped state of the art methods for assessing digital system reliability. Quantitative measures of digital system reliability are available for digital system hardware, but procedures for evaluating system level reliability (both hardware and software) are not well defined in current industry literature. However, comprehensive use of fault injection techniques for providing critical data toward evaluating digital system dependability may reduce software reliability uncertainties.

The conduct of fault injection campaigns often yields more information than just quantifying the fault tolerance aspects of a system; it also is a means to circumspect and comprehend the behaviors of complex fault tolerant I&C systems to support overall assessment activities for both the developer and the regulator. Fault injection experiments cannot be performed without gaining a deeper understanding of a system. The process itself is a learning experience, providing richer insights into how a system behaves in response to errors arising from system faults. The inclusion of fault injection information into review processes and PRA activities can enlighten the review processes of digital I&C systems. Finally, the process of conducting fault injection with each other: what the system is supposed to do, and what it actually does. This information is essential for anticipating system behaviors, performing verification and validation (V&V) activities, and conducting methodical system evaluations.

This report describes an important step toward developing a systematic method of evaluating digital system dependability. Volume 1 presents a broad and in-depth development of a digital system dependability methodology, and the requirements and challenges of performing fault injections on digital I&C systems. The process developed in this research project was applied to two digital systems that modeled nuclear power plant safety functions. The results of this phase of the research are described in volume 2 and volume 3. The cumulative findings and recommendations of both applications of the methodology and application of the generalized results to broader classes of digital I&C systems are discussed in volume 4.

| Section | <u>n</u>                                                                         | <u>P</u>                                                                      | age |

|---------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|

| ABST    | RACT.                                                                            |                                                                               | iii |

| FORE    | WORD                                                                             |                                                                               | V   |

| LIST C  | )F FIG                                                                           | URES                                                                          | ix  |

|         |                                                                                  | ILES                                                                          |     |

|         |                                                                                  | AND ABBREVIATIONS                                                             |     |

| 1.      | INTRO                                                                            | DDUCTION                                                                      | 1   |

|         | 1.1.                                                                             | Background                                                                    |     |

|         | 1.2.                                                                             | Purpose                                                                       |     |

|         | 1.3.                                                                             | Background and Motivation                                                     |     |

|         | 1.4.                                                                             | Relevance of Research with Respect to Regulatory Guidance                     |     |

|         | 1.5.                                                                             | Project Organization and Timeline                                             |     |

|         | 1.6.                                                                             | Organization of this Report                                                   |     |

|         | 1.7.                                                                             | Overview of Fault Injection                                                   |     |

|         | 1.7.                                                                             | •                                                                             | 0   |

|         | 1.0.                                                                             | Overview of the Fault Injection-based Dependability Assessment                | 10  |

|         | 10                                                                               | Methodology                                                                   |     |

|         | 1.9.                                                                             | References                                                                    | 19  |

| 2.      | RESE                                                                             | ARCH METHODOLOGY                                                              | 21  |

|         | 2.1.                                                                             | Overview                                                                      |     |

|         | 2.2.                                                                             | Identification and Selection of Appropriate Fault Injection Methods for       |     |

|         |                                                                                  | Benchmark System II                                                           |     |

|         | 2.3.                                                                             | High Performance Fault Injection for Digital I&C Systems                      |     |

|         | 2.4.                                                                             | Development of the RPS Application                                            |     |

|         | 2.5.                                                                             | Analysis of Measurement Practices and Uncertainty for Fault Injection         |     |

|         | 2.6.                                                                             | Development of Techniques to Support Function Block Fault List Generation.    |     |

|         | 2.7.                                                                             | Conduct Fault Injection Campaigns on Benchmark System II                      | 24  |

|         | 2.8.                                                                             | References                                                                    | 25  |

| 3.      | Descr                                                                            | iption of Benchmark System II and RPS Configuration                           | 27  |

| 0.      | 3.1.                                                                             | Introduction                                                                  |     |

|         | 3.2.                                                                             | Benchmark System II                                                           |     |

|         | 3.3.                                                                             | Architecture and System Description of Benchmark System II                    |     |

|         | 3.4.                                                                             | RPS Configuration for Benchmark System II                                     |     |

| 4.      | Identi                                                                           | fightion and Coloption of Foult Injection Techniques for Denshmark Queters II | 20  |

| 4.      |                                                                                  | fication and Selection of Fault Injection Techniques for Benchmark System II  |     |

|         | 4.1.                                                                             | Introduction                                                                  |     |

|         | 4.2.                                                                             | Identification of Fault Injection Methods for Benchmark System II             |     |

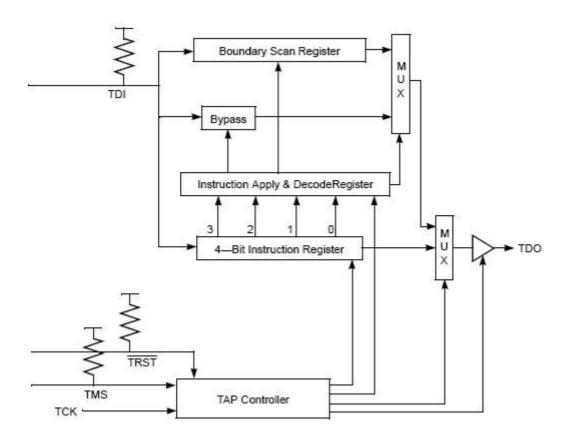

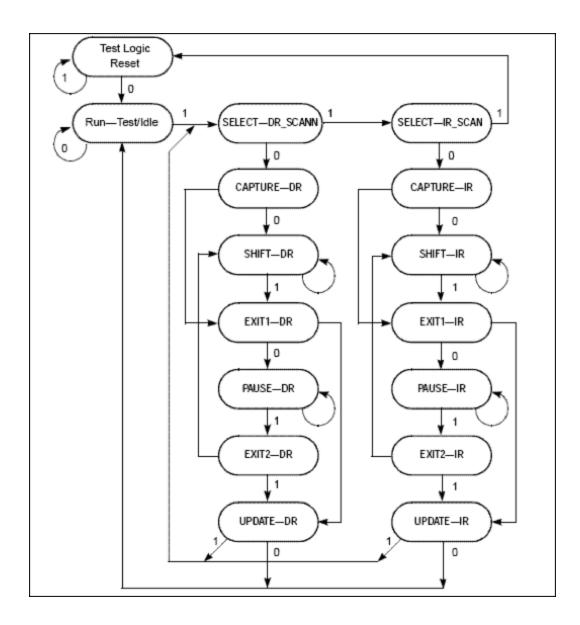

|         | 4.3.                                                                             | IEEE 1149.1 JTAG Based Fault Injection                                        |     |

|         | 4.4.                                                                             | OCD-based Fault Injection                                                     | 43  |

|         | 4.5.                                                                             | Software Implemented Fault Injection (SWIFI)                                  |     |

|         | 4.6.                                                                             | Summary of Fault Injection Techniques for Benchmark System II                 |     |

|         | 4.7.                                                                             | References                                                                    | 46  |

| 5.      | Development of a High Performance Fault Injection Module for Digital I&C Systems |                                                                               |     |

| 0.      | 5.1.                                                                             | Introduction                                                                  |     |

|         | 5.2.                                                                             | Motivation                                                                    |     |

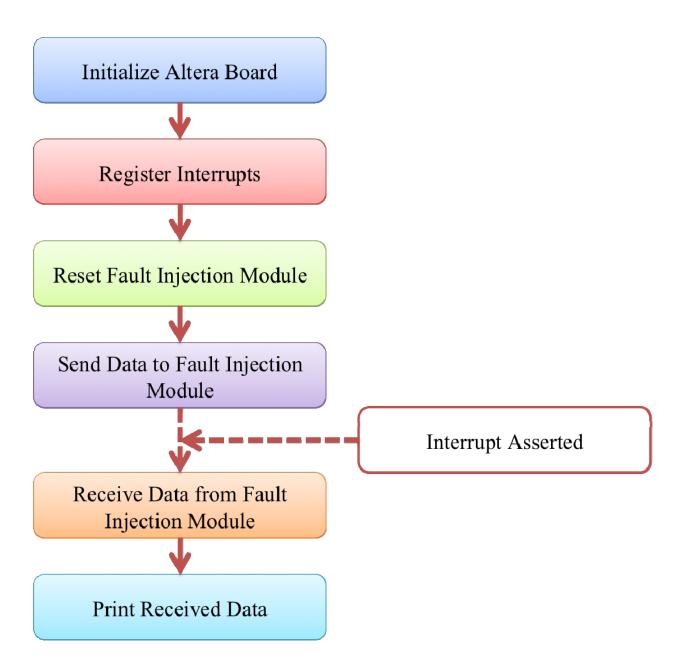

|         | 5.3.                                                                             | Design of the High Performance Fault Injector                                 |     |

|         | 5.4.                                                                             | Design of FPGA-based High Performance Adaptable Fault Injection               |     |

|         | 5.5.                                                                             | FPGA Design Tools for Realizing the Design                                    |     |

## TABLE OF CONTENTS

## TABLE OF CONTENTS (continued)

| Section                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                   | <u>Page</u>                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 5.6.<br>5.7.<br>5.8.<br>5.9.                                                                                                                                                                        | Design Challenges<br>Multi Fault Injection Capability<br>Performance Measurements<br>Bibliography                                                                                                                                                                                                                                 | 64<br>65                                                             |

| <ul> <li>6. Char</li> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> </ul>                                                                                                   | acterization of Uncertainty Sources for Fault Injection<br>Introduction<br>Background<br>Sources of Uncertainty<br>Open Issues<br>Bibliography                                                                                                                                                                                    | 69<br>69<br>70<br>74                                                 |

| 7. Integ<br>7.1.<br>7.2.<br>7.3.<br>7.4.<br>7.5.<br>7.6.<br>7.7.<br>7.8.                                                                                                                            | ration of the Benchmark System II into the UNIFI Fault Injection Environment<br>Introduction<br>Overview of UNIFI<br>Configuring and Selecting a Fault Injector<br>Set up of Fault Injection Campaigns<br>Benchmark System II Test Configuration<br>Measurement Revisited<br>Pre-fault Injection Analysis Revisited<br>References | 75<br>75<br>77<br>78<br>81<br>87<br>87                               |

| <ul> <li>8. Appl</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> <li>8.5.</li> <li>8.6.</li> <li>8.7.</li> <li>8.8.</li> <li>8.9.</li> <li>8.10</li> <li>8.11</li> <li>8.12</li> </ul> | Application of the Fault Injection Data to Benchmark System II<br>Safety Models                                                                                                                                                                                                                                                   | 93<br>93<br>95<br>97<br>98<br>103<br>105<br>107<br>112<br>112<br>113 |

| 9. Sum<br>9.1.<br>9.2.                                                                                                                                                                              | mary, Findings, and Conclusions<br>Summary of Key Activities and Results<br>Conclusions                                                                                                                                                                                                                                           | 123                                                                  |

## **LIST OF FIGURES**

| <u>Figure</u> |                                                                                                       | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------------|-------------|

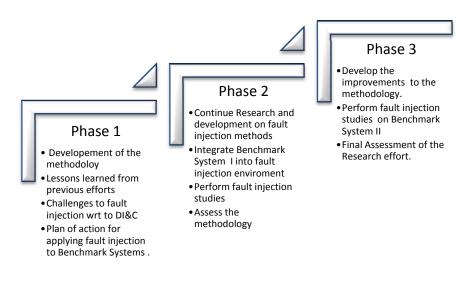

| 1-1           | Phases and activities of the research effort                                                          | 7           |

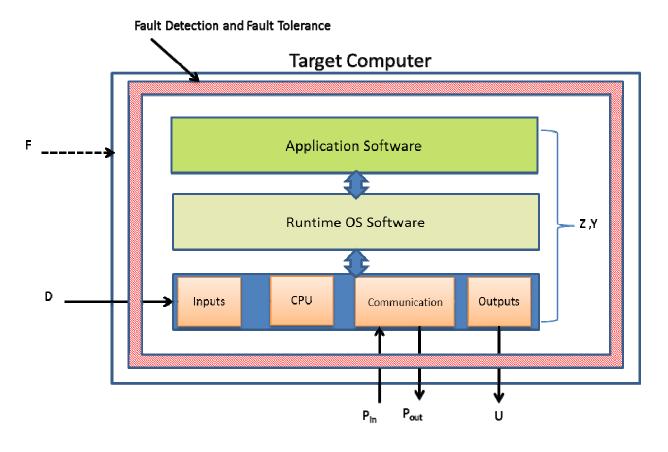

| 1-2           | Fault injection model for digital I&C                                                                 | 9           |

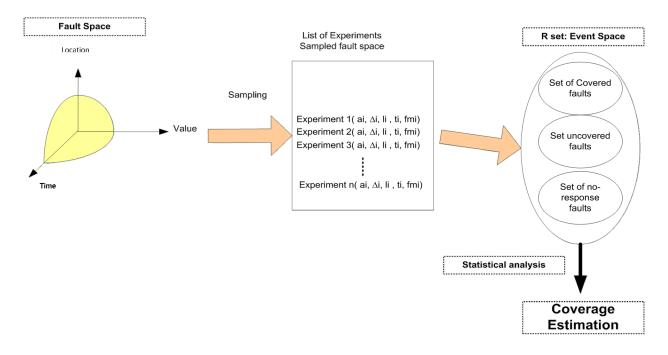

| 1-3           | Fault injection experiment                                                                            | 10          |

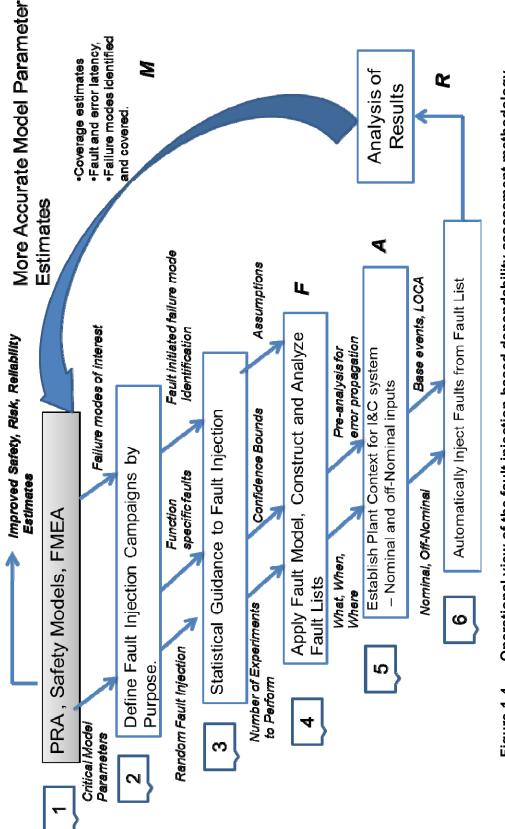

| 1-4           | Operational view of the fault injection-based dependability assessment                                |             |

|               | methodology                                                                                           |             |

| 1-5           | Fault model classes for benchmark digital I&C systems                                                 |             |

| 1-6           | UNIFI Fault Injection Environment                                                                     |             |

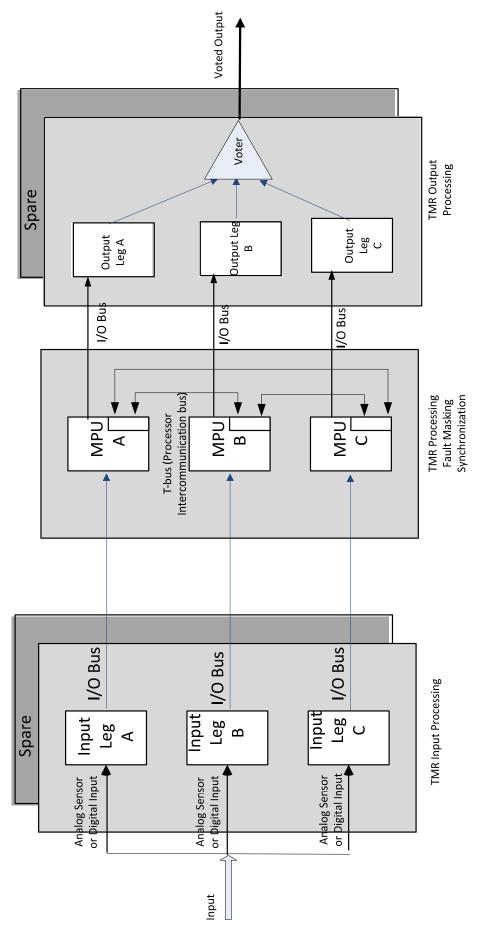

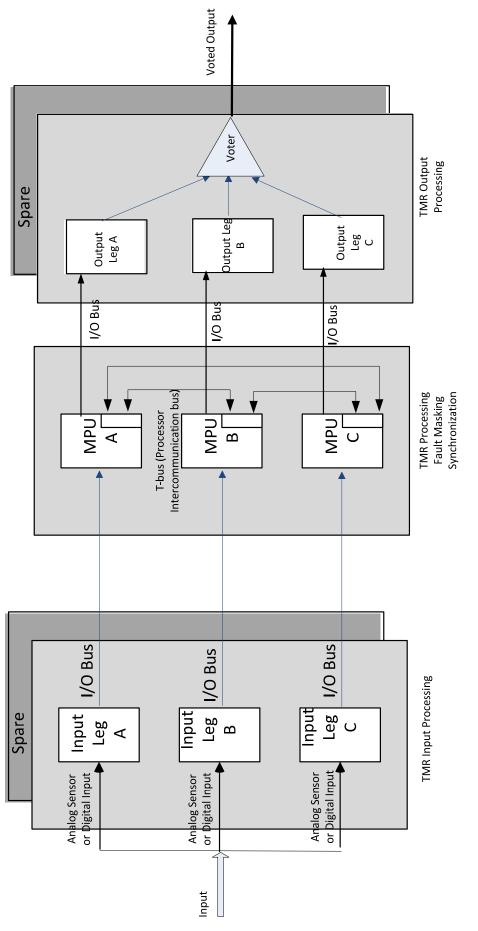

| 3-1           | Benchmark System II architecture and configuration                                                    |             |

| 3-2           | Benchmark System II detailed architecture                                                             |             |

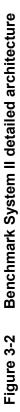

| 3-3           | Benchmark System II sub-systems targeted for fault injection                                          | 33          |

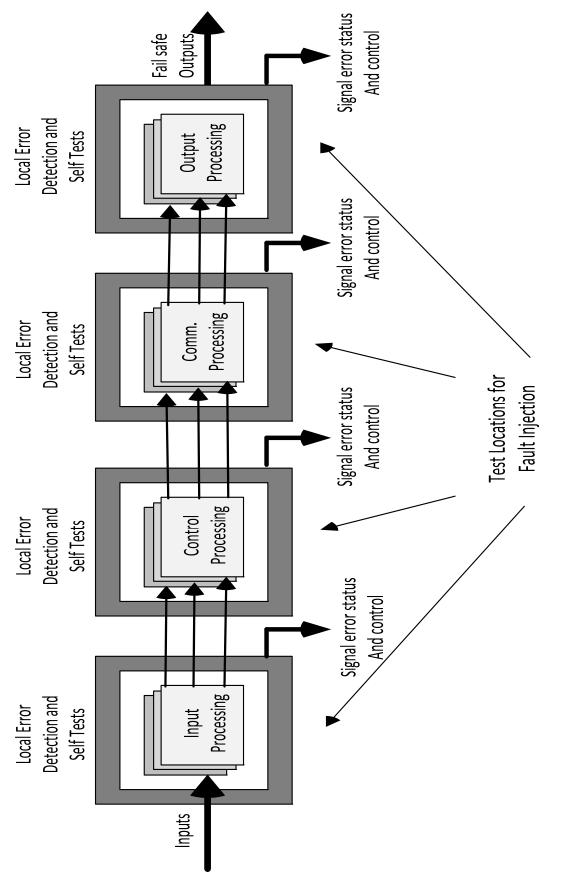

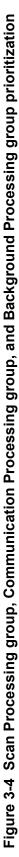

| 3-4           | Scan Processing group, Communication Processing group, and Background Processing group prioritization | 35          |

| 3-5           | Channel A RPS for Benchmark System II                                                                 |             |

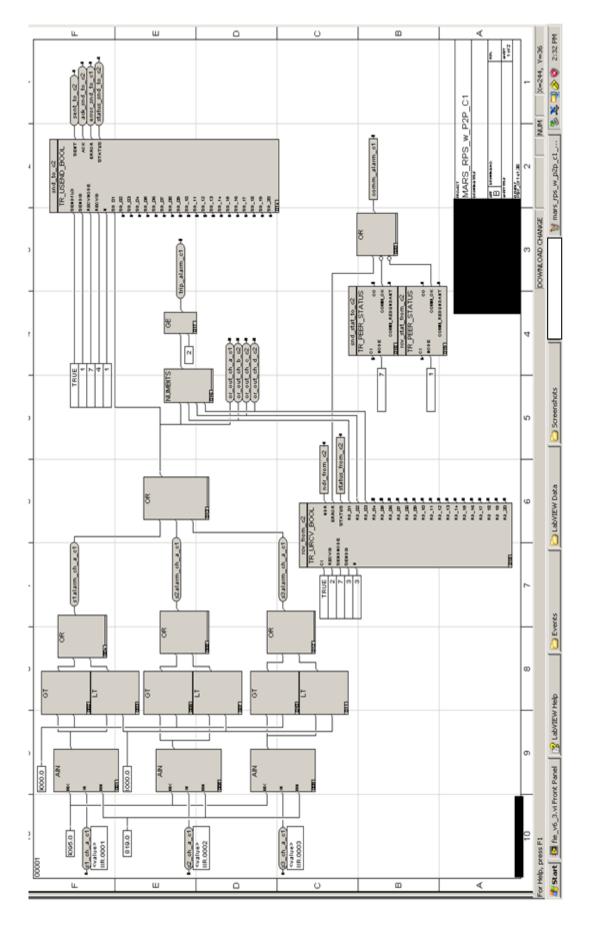

| 5-1           | Conceptual design of the FPGA-based HiPeFI                                                            |             |

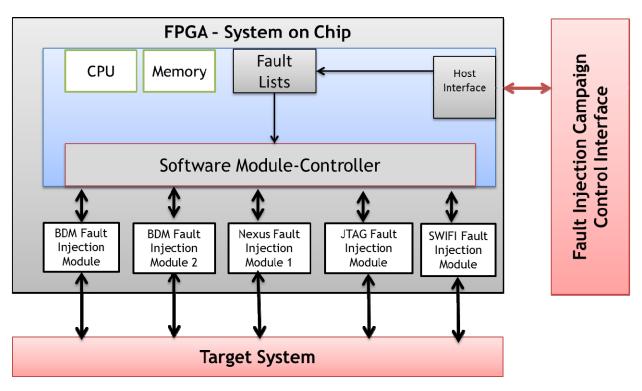

| 5-2           | FPGA-based HiPeFI architecture final design for Benchmark System II                                   |             |

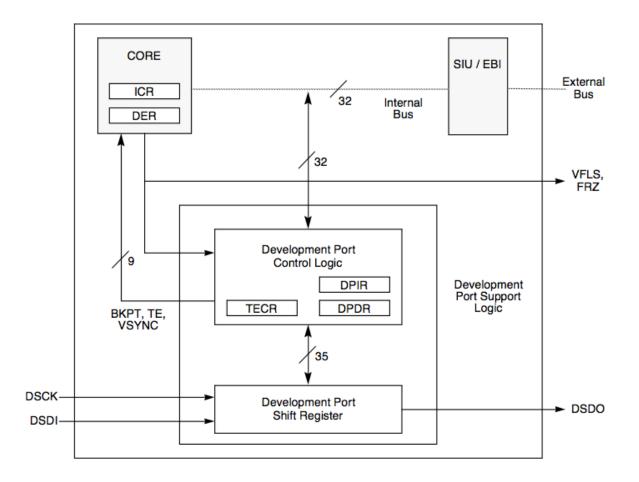

| 5-3           | BDM functional diagram of the MPC860 Debug Mode support                                               |             |

| 5-4           | Physical representation of the BDM port                                                               |             |

| 5-5           | JTAG TAP controller test logic diagram                                                                |             |

| 5-6           | JTAG TAP controller state machine                                                                     |             |

| 5-7           | Implemented software algorithm for executing BDM-based fault injection                                |             |

| 7-1           | UNIFI fault injection environment                                                                     |             |

| 7-2           | Fault list snippet                                                                                    |             |

| 7-3           | Screenshot of Master Controller window                                                                |             |

| 7-4           | Process for generating a fault list using UNIFI                                                       |             |

| 7-5           | Screenshots of the fault list generation GUI                                                          |             |

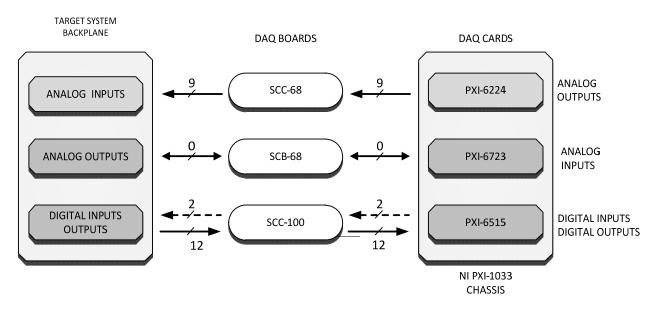

| 7-6           | Test configuration of Benchmark System II                                                             |             |

| 7-7           | Signal connections to benchmark system                                                                |             |

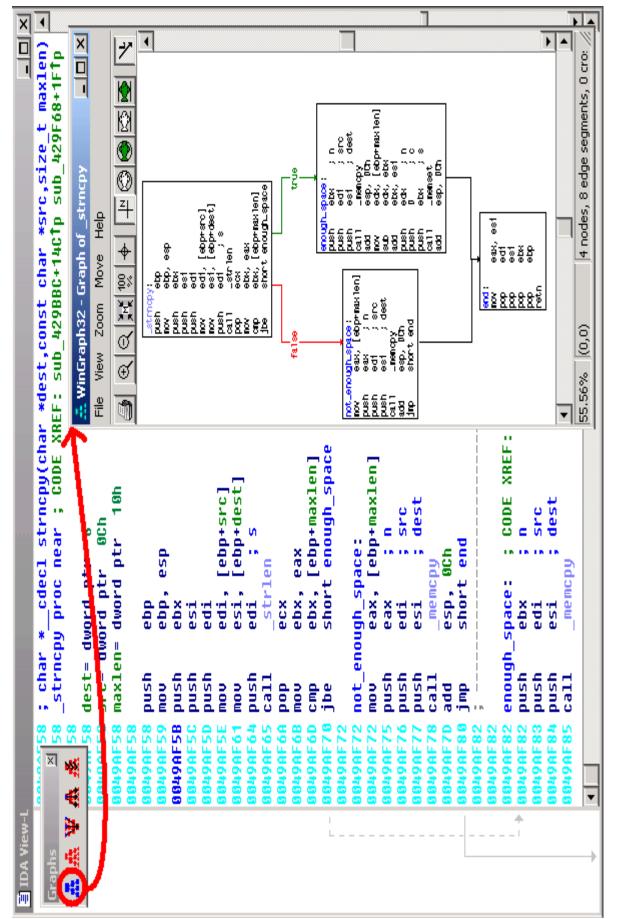

| 7-8           | Graphing binary code with IDA Pro                                                                     | 90          |

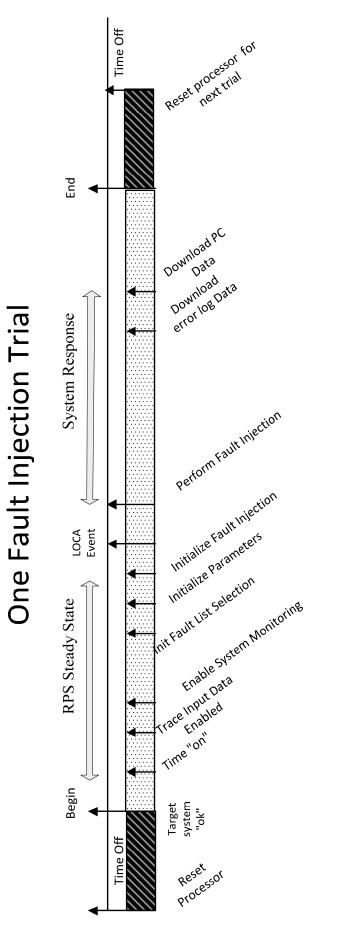

| 8-1           | Fault injection sequence for Benchmark System II                                                      |             |

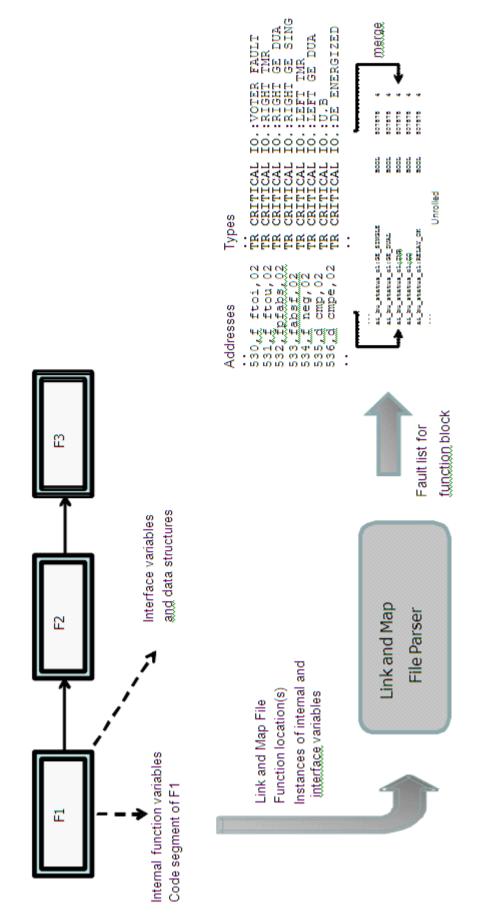

| 8-2           | Function block fault list generation                                                                  | 99          |

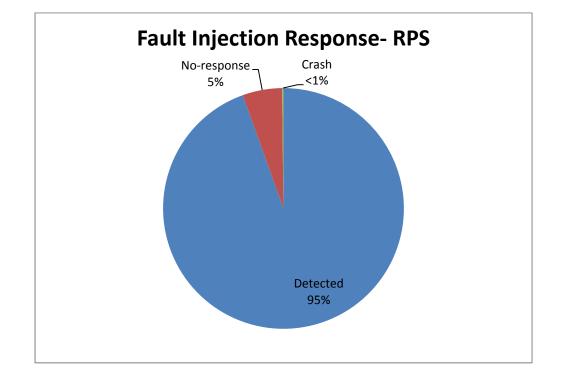

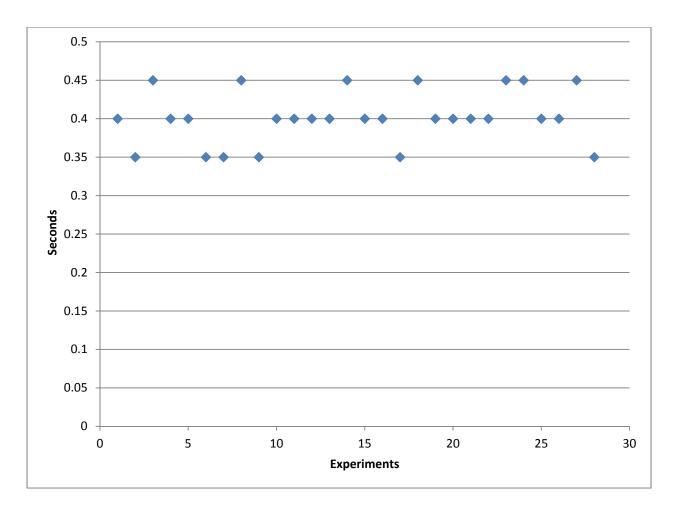

| 8-3           | Raw fault injection response data - RPS                                                               | 102         |

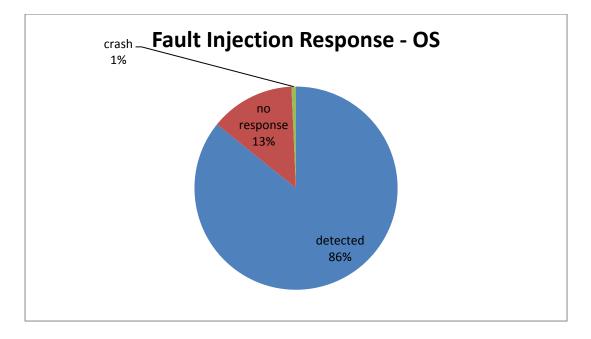

| 8-4           | Raw fault injection response data - OS                                                                | 103         |

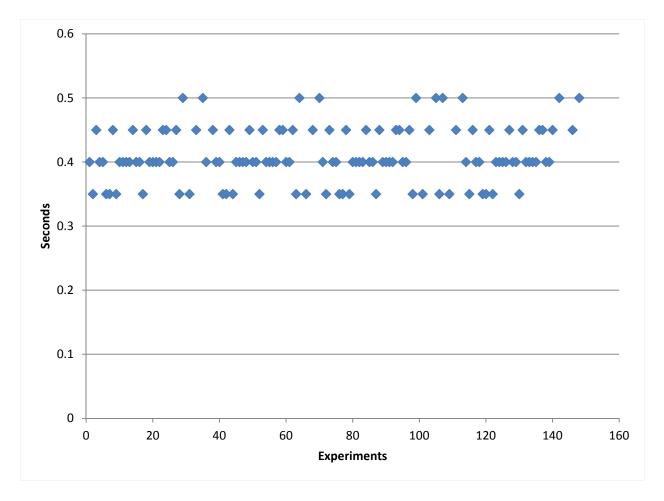

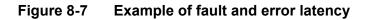

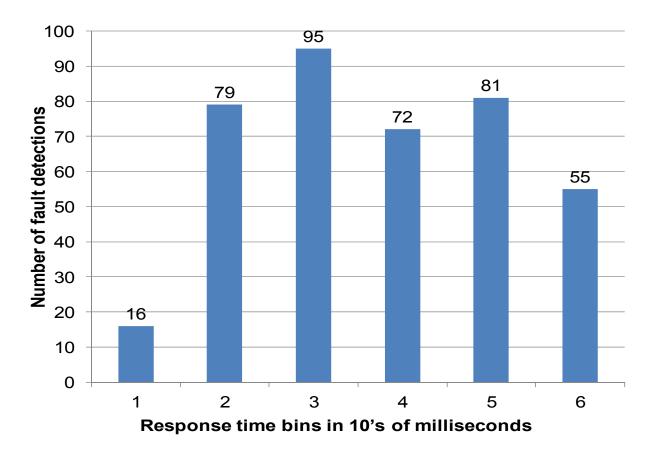

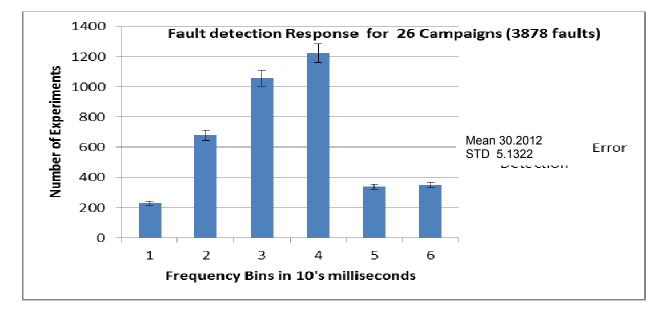

| 8-5           | Trip alarm response times (faulted)                                                                   |             |

| 8-6           | Trip alarm response times (non-faulted)                                                               | 107         |

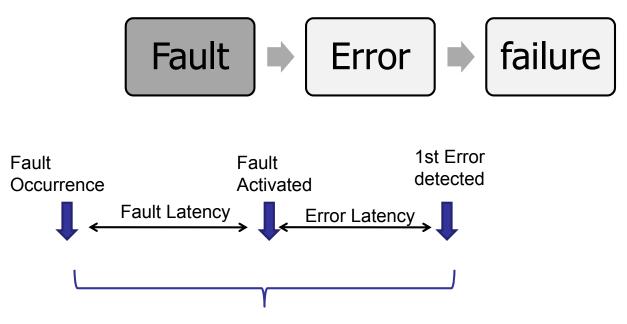

| 8-7           | Example of fault and error latency                                                                    | 108         |

| 8-8           | Error log transcript from the TRILOG server                                                           | 109         |

| 8-9           | Fault/Error latency interval time                                                                     |             |

| 8-10          | Frequency of occurrence of system fault detection responses                                           |             |

| 8-11          | Frequency of occurrence of fault latency over set of fault injection campaigns                        |             |

| 8-12          | Benchmark System II detailed architecture                                                             |             |

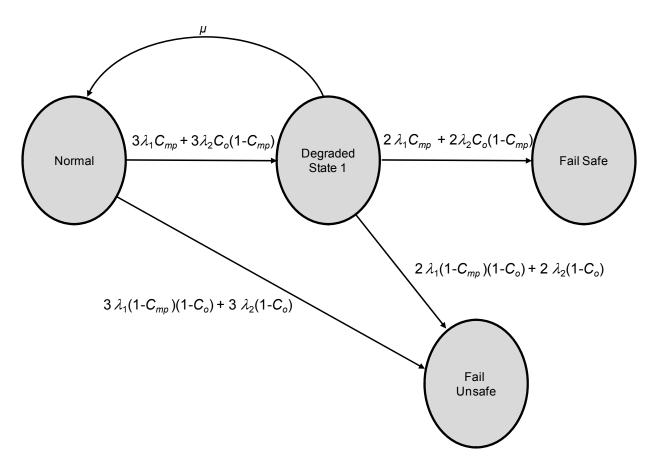

| 8-13          | Simplified Markov model of the benchmark system                                                       |             |

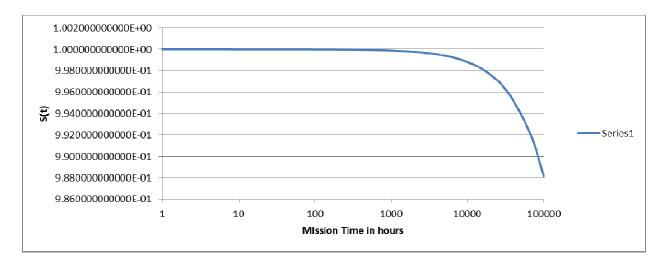

| 8-14          | Example of system safety as a function of mission time                                                |             |

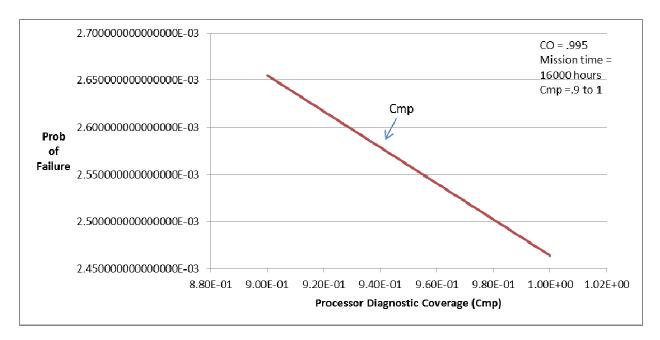

| 8-15          | Failure probability as a function of processor diagnostic coverage                                    |             |

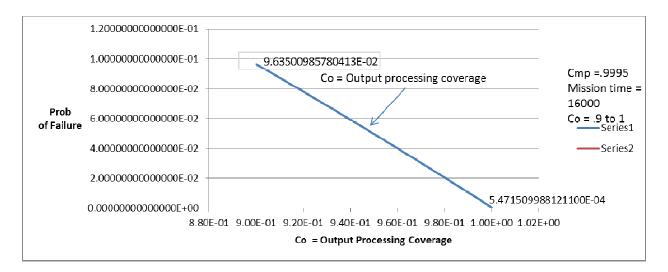

| 8-16          | Failure probability as a function of output diagnostic coverage                                       | 122         |

## LIST OF TABLES

#### Table Page 4-1 7-1 8-1 8-2 8-3 8-4 8-5 8-6

х

## ACRONYMS AND ABBREVIATIONS

| A/D<br>API<br>BDM<br>BSC<br>CFR<br>COTS<br>CPU<br>CRC<br>D/A<br>DFWCS<br>DI&C<br>DPDR<br>DPIR<br>ESFAS<br>ETM<br>FARM<br>FDIM | Analog to Digital<br>Application Programmer Interface<br>Background Debug Mode<br>Boundary Scan Chain<br>Code of Federal Regulations<br>Commercial Off-the-Shelf<br>Central Processing Unit<br>Cyclic Redundancy Check<br>Digital to Analog<br>Digital Feedwater Control System<br>Digital Instrumentation and Control<br>Development Port Data Register<br>Development Port Instruction Register<br>Engineered Safety Features Actuation System<br>Enhanced Trace Macro-cell<br>Faults, Activations, Readouts, and Measures<br>Fault Detection, Isolation, and Mitigation |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FMEA                                                                                                                          | Failure Modes and Effects Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FPGA                                                                                                                          | Field Programmable Gate Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GUI                                                                                                                           | Graphical User Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GOOFI                                                                                                                         | Generic Object Oriented Fault Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HiPeFI                                                                                                                        | High Performance Fault Injection<br>Human Machine Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HMI<br>HW                                                                                                                     | Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I&C                                                                                                                           | Instrumentation and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ICE                                                                                                                           | In Circuit Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IEC                                                                                                                           | International Electro-technical Commission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IEEE                                                                                                                          | Institute of Electrical and Electronics Engineers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IC                                                                                                                            | Integrated Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| I/O                                                                                                                           | Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOCCOM                                                                                                                        | I/O Communication Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IP                                                                                                                            | Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ISA                                                                                                                           | Instruction Set Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ISR                                                                                                                           | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| JTAG                                                                                                                          | Joint Test Action Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LOCA                                                                                                                          | Loss of Coolant Accident                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MP                                                                                                                            | Main Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MPU                                                                                                                           | Main Processor Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MTTF                                                                                                                          | Mean Time to Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NPP                                                                                                                           | Nuclear Power Plant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NRC                                                                                                                           | Nuclear Regulatory Commission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OCD                                                                                                                           | On-Chip Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OP                                                                                                                            | Operational Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OS                                                                                                                            | Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PRA                                                                                                                           | Probabilistic Risk Assessment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PXI                                                                                                                           | National Instruments Data Acquisition Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RAM                                                                                                                           | Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RPS                                                                                                                           | Reactor Protection System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RTE                                                                                                                           | Runtime Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RTOS                                                                                                                          | Real-Time Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCIFI                                                                                                                         | Scan Chain Implemented Fault Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Single Event Upset                                               |

|------------------------------------------------------------------|

| Small Modular Reactor                                            |

| Systems on a Chip                                                |

| System-on-Programmable-Chip                                      |

| Semi-Markov Unreliability Reliability Estimation                 |

| Software Implemented Fault Injection                             |

| Test Access Port                                                 |

| Test Clock                                                       |

| Test Data In                                                     |

| Test Data Out                                                    |

| Triple Modular Redundant                                         |

| Test Mode Select                                                 |

| TRAC/RELAP Advanced Computational Engine                         |

| Test Reset                                                       |

| Universal Platform-Independent Fault Injection                   |

| Universal Asynchronous Receiver/Transmitter                      |

| University of Virginia                                           |

| Volts D/C                                                        |

| Very High Speed Integrated Circuit Hardware Description Language |

| Virtual Instrument                                               |

| Verification and Validation                                      |

| Very Large Scale Integration                                     |

|                                                                  |

## 1. INTRODUCTION

## 1.1. Background

This report is Volume 3 of a multi-volume set of reports that present the cumulative efforts, findings, and results of U.S. Nuclear Regulatory Commission (NRC) contract JCN N6124 – "Digital System Dependability Performance." The reports are organized as follows:

- Volume 1 Presents a broad and in-depth development of the methodology, the requirements, and challenges of realizing fault injection on digital instrumentation and control (I&C) systems.

- Volume 2 Presents the application of the methodology to Benchmark System I.

- **Volume 3** Presents the application of the methodology to Benchmark System II- employing the lessons learned from Benchmark System I.

- **Volume 4** Presents the cumulative findings and recommendations of both applications of the methodology and generalizes the results to broader classes of digital I&C systems.

### 1.2. Purpose

This report (Volume 3) presents the findings of applying a fault injection based quantitative assessment methodology (presented in Volume 1) to a processor-based digital I&C system for the purpose of evaluating the capabilities of the method to support NRC probabilistic risk assessment (PRA) and review processes for digital I&C systems. The further purpose of this work is to help inform the development of regulatory guidance processes for digital I&C systems and potential improvements to the licensing process for digital I&C systems in nuclear power plant (NPP) operations. The work described herein broadly presents;

- (1) the development of the fault injection methods and techniques that were applied to Benchmark System II,

- (2) the development of a fault injection environment for digital I&C systems

- (3) development of pre-injection analysis methods for automatically generating fault lists for digital I&C systems,

- (4) (results of the application of the fault injection method to Benchmark System II,

- (5) the challenges to applying fault injection to contemporary digital I&C systems, and

- (6) the findings for addressing these challenges and establishing a basis for implementing fault injection to digital I&C platforms.

## 1.3. Background and Motivation

Given the revitalization of the nuclear power industry in the United States (US), there is near uniform agreement in the nuclear industry that significant technology and production challenges must be addressed to enable efficient construction of new plants and refurbishment of existing plants. These challenges are largely being driven by the need to extend the life of current operating NPPs by an additional 20 years to 30 years (up to 60 years total plant life) to meet

projected energy consumption demands while new plants are constructed and licensed to operate [Energy 2011].

Next generation NPPs and modernized plants will be fundamentally different from their predecessors. Emergent computer technology has introduced the capability of integrating information from numerous plant systems and supplying needed information to operations personnel in a timely manner that could not be envisioned when previous generation plants were designed and built. At present, numerous versions and different types of new advanced digital I&C systems are in the regulatory licensing application process. However, with the introduction of software-based and hardware description language-based I&C systems for NPP control and monitoring and new human-machine integration capabilities, potential digital failure mode issues have arisen that could adversely affect safety and security [Committee 1997]. However, the need for these digital I&C systems to be as dependable as their predecessors across a wide spectrum of threats, faults, and failures to ensure public safety is of the utmost importance.

In recent years significant effort has gone into improving safety critical system design methodologies, assessment methods, and the updating of regulatory industry standards and NRC regulatory guidelines to ensure that digital I&C systems can be designed and assessed to the high safety requirement levels required of highly critical applications. Of particular interest recently are quantitative dependability assessment methodologies that employ fault injection methods to ensure proper compliance of digital I&C system fault handling mechanisms [Arlat 1993; Yu 2004; Smith 2000; Elks 2009(a); Aldemir 2007; Smidts 2004]. The goal of a dependability assessment methodology is to provide a systematic process for characterizing the safety and performance behavior of embedded systems (e.g. digital I&C systems) in the presence of faults.

Dependability evaluation involves the study of failures and errors and their potential impact on system attributes such as reliability, safety and security. Very often the nature of failures or system crashes and long error latency often make it difficult to identify the causes of failures in the operational environment. Thus, it is particularly difficult to recreate a failure scenario for large, complex systems just from system failure logs alone. To identify and understand potential failures, the use of an experiment-based or measurement based approach for studying the dependability of a system is gaining acceptance in the nuclear industry for better understanding the effects of errors and failures to promote an informed understanding of risk. Such an approach is useful not only during the concept and design phases, but also during licensing review activities.

From a practical point of view, most digital I&C systems are designed as safety critical systems employing extensive fault detection/tolerance and design diversity features to ensure proper operational and fail safe behavior in the event of a system failure. For example, Fault Detection, Isolation, and Mitigation (FDIM) software and online diagnostic functions of the benchmark systems in this research effort account for as much as 40 to 50 percent of the executable system software code [Barton 1990; Palumbo 1986; Young 1989]. This code is rarely challenged during normal operations because faults and failures are an infrequent occurrence. This FDIM code is vital toward system dependability and safety compliance, and can only be effectively tested and validated by realistic fault injection campaigns.

## **1.4.** Relevance of Research with Respect to Regulatory Guidance

The NRC has a comprehensive set of regulatory guidelines for reviewing and assessing the safety and functionality of digital I&C systems. The NRC PRA technical community has not yet agreed on how to model the reliability of digital systems in the context of PRA and the level of

detail that digital systems require in reliability modeling. Nonetheless, it is clear that PRA models must adequately represent the complex system interactions that can contribute to digital system failure modes. The essential research aim of the PRA technical community is to accurately model digital I&C system behaviors to take into account interactions of the system fault handling behaviors, coverage of fault tolerance features, and the view of the system as an integrated software and hardware system.

Fault injection is a formal-based process to collect evidence to gauge the dependability of safety functions associated with I&C systems that has an underlying mathematical theory (with explicitly stated assumptions) that allows one to place stronger justification or refutation on claims of the overall safety of an I&C system. Fault injection as part of a quantitative assessment process is a robust testing process that can support verification and validation (V&V) and quality assurance activities to gather evidence that the digital I&C system can perform its safety functions in the presence of faulted and failure conditions in compliance with NRC regulations. In addition, those aspects of Appendix B of Title 10 of the Code of Federal Regulations (CFR), Part 50 (10 CFR 50), the NRC Standard Review Plan (NUREG-0800), and other relevant guidelines that address requirements for testing processes, methods and evidence to support safety function operational effectiveness are clear candidates for the application of fault injection methods.

### 1.4.1. Relationship to NRC Research Activities

The research conducted under this contract was done with the consideration of previous and on-going research efforts related to the safety and reliability assessment of digital I&C systems. Accordingly, the research effort was attentive of complementary research efforts and how those efforts could benefit from the work accomplished through this effort. Specifically, the researchers recognized that the products developed from this research could have the potential to be used in other research efforts. Therefore, the researchers endeavored to catalog research findings in way that promoted broader relevance and helpful information for other research efforts.

#### 1.4.2. Research Objectives

The overall objective of this research was to develop a body of evidence to inform the development of regulatory guidance processes for digital I&C systems and potentially improve the licensing process of digital I&C systems in NPP operations. In support of this objective the research investigated the effectiveness of fault injection (as applied to digital I&C systems) for providing critical parameters and information required by PRA and reliability assessment processes. The results and findings of this effort are aimed at assisting NRC staff determine when, where and how fault injection-based methodologies can best fit in the overall license review process.

The major goals of the research effort are:

#### **Objective 1**

Demonstrate the effectiveness of the University of Virginia (UVA) quantitative safety assessment process on commercial safety grade I&C systems executing reactor protection applications with respect to a simulated NPP safety system design.

#### **Objective 2**

Identify, document, and develop improvements to the fault injection-based process that make it easier and more effective to apply to a wider spectrum of digital I&C systems.

#### **Objective 3**

Document the limitations, sensitive assumptions, and implementation challenges that would encumber the application of fault injection processes for digital I&C systems. Also document the quantitative and qualitative results that can be obtained through application of the assessment process, and provide the technical basis upon which NRC can establish the regulatory requirements for safety-related digital systems, including the acceptance criteria and regulatory guidance documents.

#### Secondary Objective 1

Assess the level of effort and cost for implementing fault injection capability in a vendor or licensee environment.

#### Secondary Objective 2

Identify and develop innovative fault injection methods that would make fault injection more efficient and easier to adopt by NRC and the nuclear industry.

The scope of this work is targeted at safety critical digital I&C systems, but applies to non-safety related systems as well. The target benchmark systems were configured to be representative of a four-channel Reactor Protection System (RPS) system, but were limited in scale due to budget constraints on equipment availability. Therefore, the benchmark systems lacked some redundant hardware modules that would normally be found in an actual RPS. The overall complexity and configuration of the system was sufficient to stress the methodology, which was the objective of the research effort. The specific benchmark system configuration described in this report unless otherwise stated.

The methodology that was developed and applied in this research effort is part of a larger comprehensive assessment and review process, and is not intended to be interpreted as a "replacement" for existing processes. Rather, the methodology should be viewed as a complementary method to support existing and emerging design assurance and license review processes in an effort to establish more efficient, repeatable, and objective design assessment and review processes.

Fault injection-based methods are but one part of a comprehensive process of estimating the reliability of digital systems (hardware and software) for the purpose of PRA applications. From the highest level perspective, reliability estimation requires (1) the knowledge of the likelihood of faults (software or hardware) and (2) the consequence of activating these faults in the system context. Fault injection methods are most useful in characterizing system responses to activated faults - the second requirement. That is, providing empirical knowledge on the triggering, detection, tolerance, and propagation of errors due to software or hardware faults in the system. As such, the methodology developed and presented in this set of reports is aimed at providing empirical data in support of estimating system fault response data, such as fault detection, error propagation, fault latency, and timing delays.

#### 1.4.3. Work Tasks for Phase II

Section 9 of Volume 1 presents the basic research plan of the project, which was used as a guide to realize the UVA fault injection-based dependability assessment methodology on the benchmark systems. This plan has two categories of tasks. The first task category includes items that require additional research and development to determine their potential for implementation. As such, this was on-going work for the project. The second category comprises tasks that needed little or no additional research effort to implement to determine their overall effectiveness. The second category should be viewed as items that needed to be accomplished in order to support the overall research objectives.

#### 1.4.3.1. Research Oriented Tasks

The research oriented tasks listed below are specifically tied to key challenges identified in Section 8 of Volume 1 and findings from Volume 2.

**High performance fault injection** – Lessons learned from applying fault injection to Benchmark System I suggest a critical need for fault injection techniques to support various fault models for fault injection in a manner that is minimally intrusive, controllable, repeatable and reproducible. This task investigated, designed, developed, and implemented new methods to achieve these goals.

**Data collection and analysis** – In support of better measurement practices, the research investigated the requirements for data collection from the benchmark systems. This included a thorough understanding of the relationship between the error messages from the target benchmark system and the underlying error detection and fault tolerant mechanisms in the target benchmark systems. Prior experience had shown that vast amounts of data are the norm during long fault injection campaigns. Finding methods to manage the data, establish relationships between the data sets, and reduce the data sets to essential attributes were key to an effective analysis process.

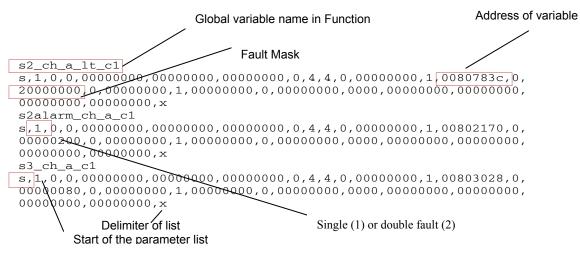

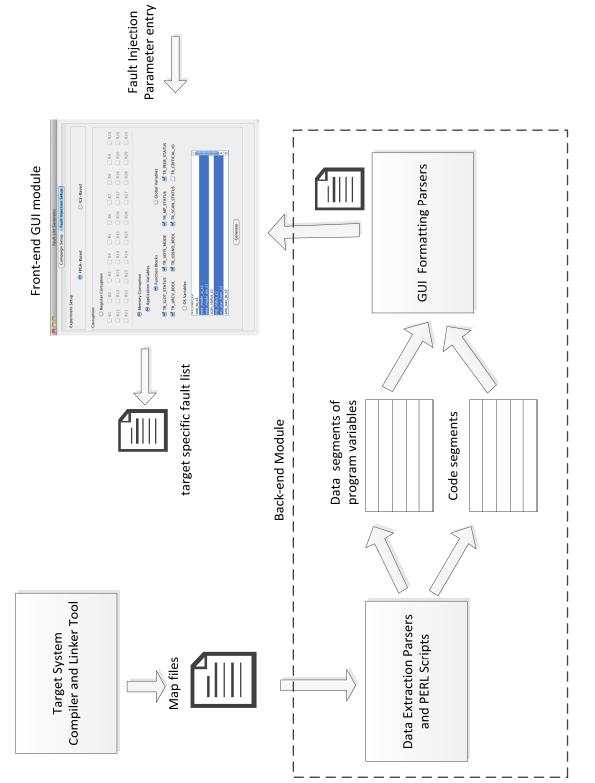

**Enhanced fault list generation** - Generating fault lists for a fault injection experiment or campaign is a critical activity for fault injection. Function block fault list generation extends the capabilities of the map file fault list generation presented in Volume 2 by identifying high-level function block code and data segments in the locatable image files. Nearly all digital I&C systems in proposed nuclear power plant safety applications use a function block software programming environment that employs libraries of pre-determined function blocks needed to design a particular application. The user or software engineer builds the application from these libraries of function blocks. Regulators, designers, and safety reviewers understand the system from this point of view, so it was important to provide the capability to guide fault injection campaigns from this perspective.

**Operational profile generation** – Operational profiles and workloads of the target system are required to set the operational and environmental context of the system. The operational profiles must be representative of the different system configurations and workloads that would be experienced in actual field operations. In order to provide a diverse and representative set of operational profiles for the target system, the use of high fidelity NPP simulator tools to generate nominal, off-nominal, and accident event profiles is a promising approach. To support this task, the research effort developed a process for integrating TRAC/RELAP Advanced Computational Engine (TRACE) thermo-hydraulic NPP simulator results into the UVA fault injection environment so that real time process data from the simulator could be used to drive the inputs of the target benchmark system under various conditions and modes.

#### 1.4.3.2. Research Support Tasks

Research tasks are necessary to support research activities using Benchmark System II. As in previous fault injection process efforts, the amount of time to design, develop, test, and integrate various fault injection components and then interface these components into the target benchmark system can be significant. These research support tasks are:

*Training and experience* – To effectively apply fault injection to complex digital I&C systems of the type found in the benchmark systems, the research staff at UVA required professional training by the respective vendors of the benchmark system platforms. Once this training was

completed, the staff required time to gain additional experience on the systems to fully understand the details of the system platforms from various points of view.

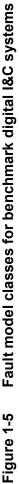

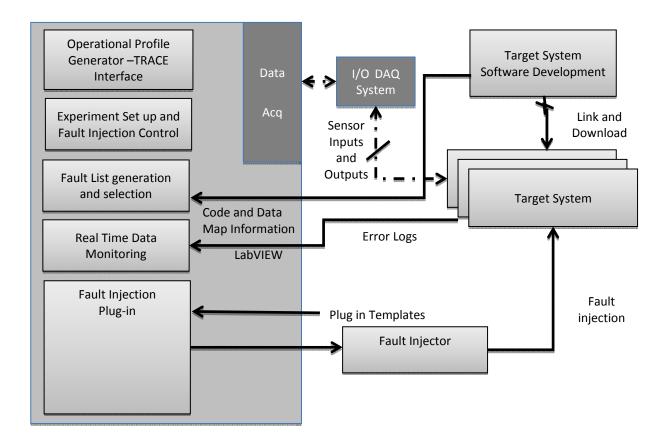

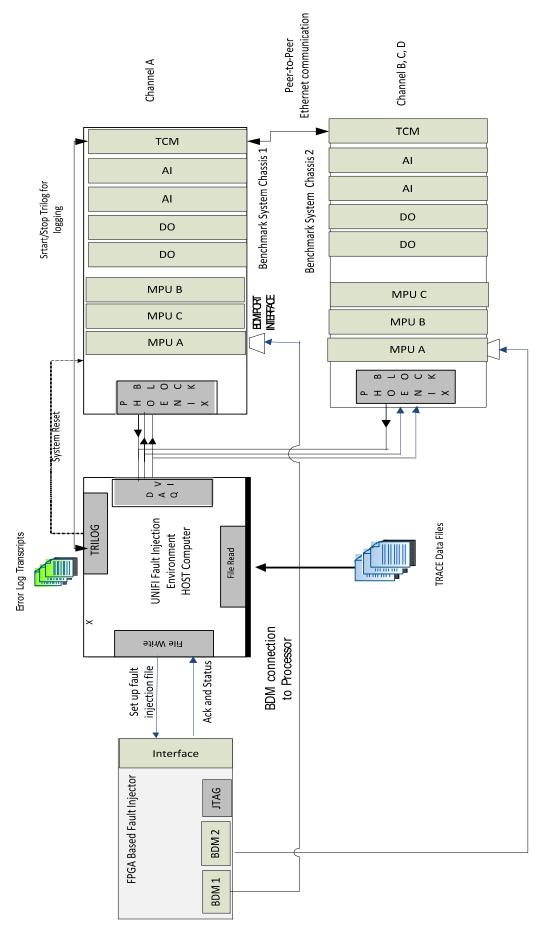

*Fault injection environment* – A well-formed fault injection environment is one of the most important aspects of a fault injection-based methodology to support credible, repeatable, and controllable fault injection campaigns. The fault injection environment plays a crucial role in the data collection and measurement of the responses, which are important to produce the measures of dependability (e.g. coverage and error latency).

The user must have the ability to manage the types of faults to be injected into the system, where they are injected, how they are injected, and when they are injected. Additionally, the responses to the fault injections must be acquired in a manner that allows the responses to be traced back to the faults so that any fault injection trial can be repeated as needed to reproduce the system response.

In addition to the basic functional requirements for a fault injection, effective fault injection environments must also be practical to implement and use, adaptable to changing technology, and supportable. Several development goals for the fault injection environment to allow for adaptability for different I&C systems include:

- Flexibility for a wide variety of applications

- Easy to use and familiar to the engineering culture

- Industry-grade, supportable, and open source

- Modular

- Extensible

- Evolutionary